# TOWARDS HIGHLY EFFICIENT MONOLITHIC DC/DC CONVERTER

Piyush Keshri 3<sup>rd</sup> Year Undergraduate Student Indian Institute of Technology Kanpur, India Tutor: Prof. Heiner Ryssel

# Outline

- Introduction

- Types of Switching Regulators

- Buck Converter

- Modes of operation of Buck converter

- Boost converter

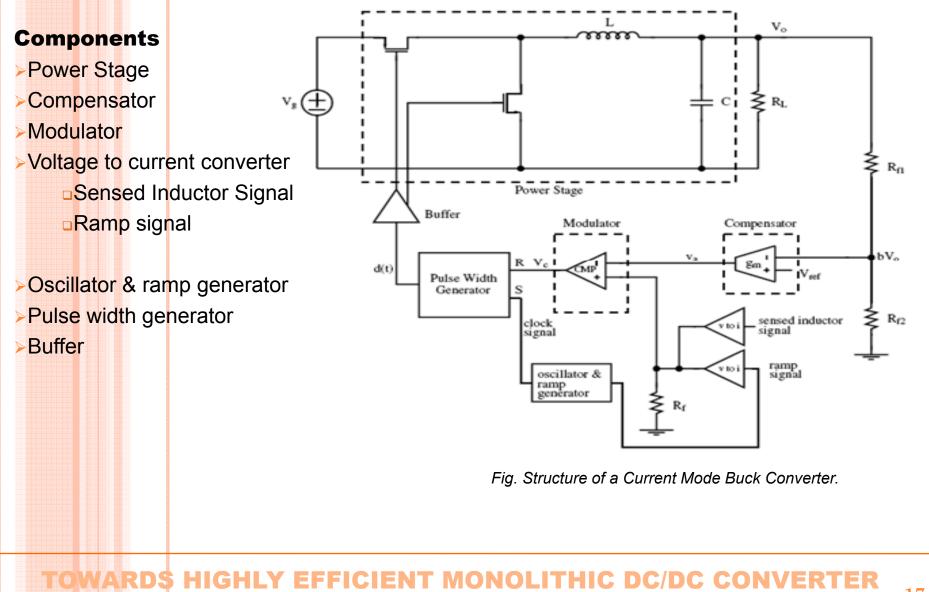

- Structure of monolithic Converter

- Method of operation of various parts of the converter.

- Integration of Inductor on chip

- Integration of capacitor on chip

- Power losses in the converter

- Power flow analysis

- Issues in monolithic DC/DC converter

- Techniques to improve performance

- Compensated Error amplifier

- Light load efficiency

## Introduction

# What is DC/DC Converter?

A device that accepts a DC input voltage

Produces a DC output voltage

# Used to provide:

- Noise isolation

- Power bus regulation etc.

- Output at different voltage level

- Wide Input voltage range

- Constant Output Voltage

- Galvanic Isolation

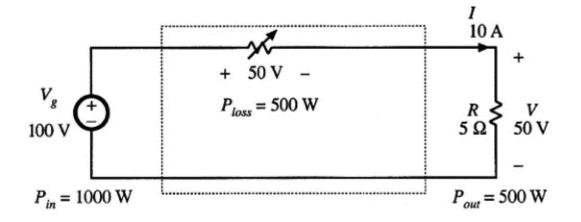

## **Linear Regulator**

- Extremely inefficient (depending on voltage drop!)

- High heat dissipation

- Bulky and expensive heat sink

- Impossible for SOC design

- Reduce battery life

- No switching noise

## **Switching Regulator**

- **Takes small chunk of energy from i/p & transfer to the o/p**

- Uses electrical switch & controller to regulate rate of energy

- High efficiency

- Used in portable devices- cell phones, laptops, robots etc.

- Smaller size

- Lower heat generation

- Suitable for on chip design

### **Disadvantages of Switching Regulator**

- Complex System Design

- High frequency electrical noise

- Ripple voltage at switching frequency

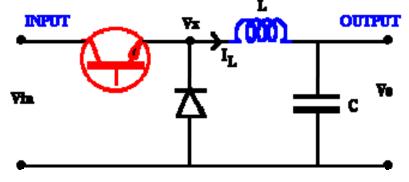

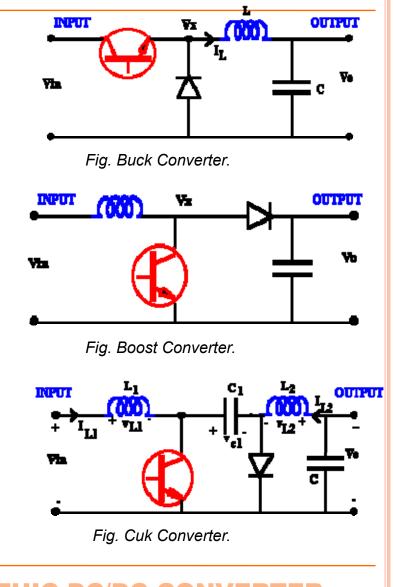

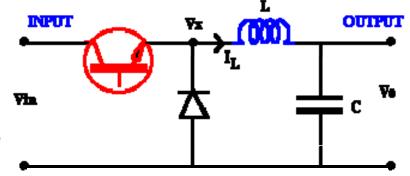

Fig. Buck Converter.

## **Types of Switch Mode Regulators**

- Buck Converter- Step-down converter

- Boost Converter- Step-up converter

- Cuk Converter

- Isolated converters:

- Flyback converter

- Forward converter

- **Full-** / Half bridge converter

101010

TOWARD\$ HIGHLY EFFICIENT MONOLITHIC DC/DC CONVERTER

Fig. Flyback Converter.

OUTPUT

When Transistor 'ON'

Inductor current rises

### When Transistor 'OFF'

Current through inductor passes through the diode

### Modes of operation:

Continuous Mode

Transition b\w Continuous & Discontinuous Mode

Discontinuous Mode

Fig. Circuit Layout Of Buck Converter

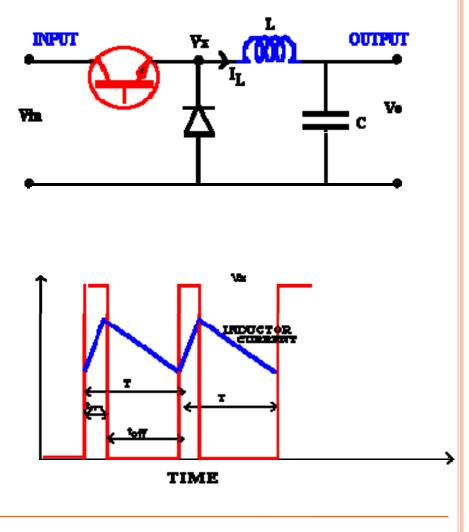

### **Continuous Mode**

The change in current satisfies,

$$di = \int_{ON} (Vx - Vo) dt + \int_{OFF} (Vx - Vo) dt$$

For steady state operation,

$$di = 0 = \int_{ON} (Vx - Vo) dt + \int_{OFF} (Vx - Vo) dt$$

Hence,

$$\frac{Vo}{Vin} = \frac{ton}{T}$$

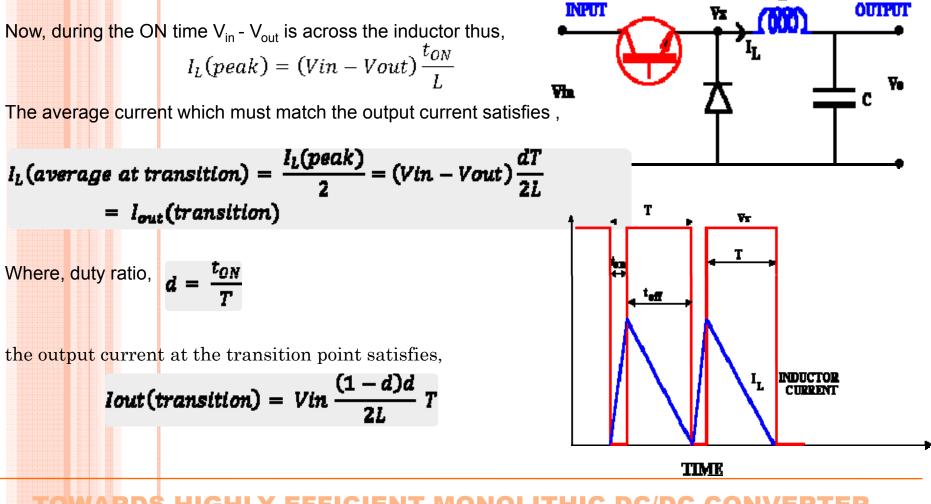

### **Transition** b\w Continuous & Discontinuous Mode

Inductor current just goes to zero.

**OWARD\$ HIGHLY EFFICIENT MONOLITHIC DC/DC CONVERTEI**

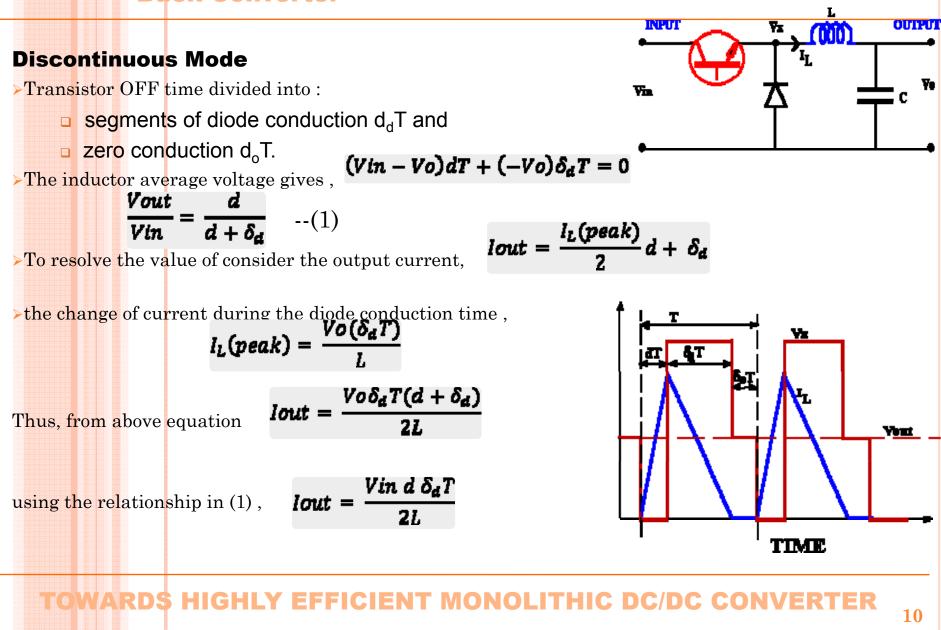

### **Discontinuous Mode**

Solving for the diode conduction ,

$$\delta_d = \frac{2L \, lout}{V in \, d \, T}$$

The output voltage is thus given as ,

$$\frac{Vout}{V!n} = \frac{d^2}{d^2 + (\frac{2L \ lout}{Vin \ T})}$$

> defining k\* = 2L/(V<sub>in</sub> T),

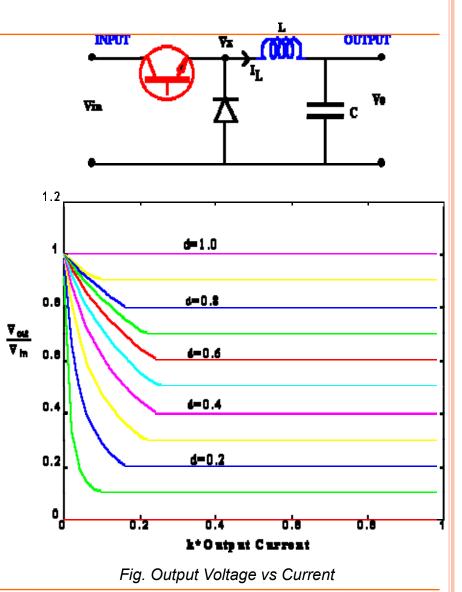

### Output voltage vs. Current

High O/p current voltage ratio depends on the duty ratio "d".

Low currents discontinuous operation tends to increase o/p voltage of the converter towards V<sub>in</sub>.

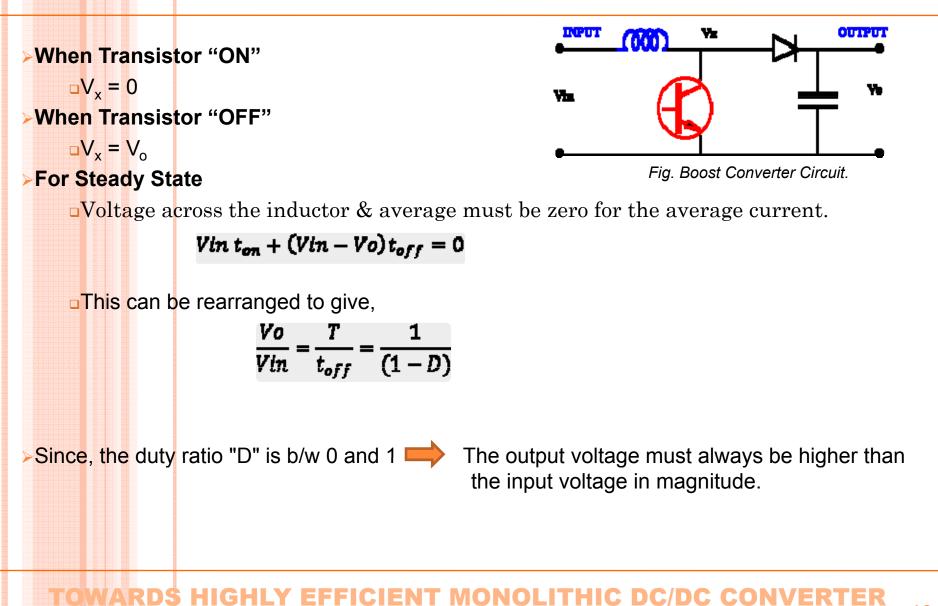

### **Boost Converter**

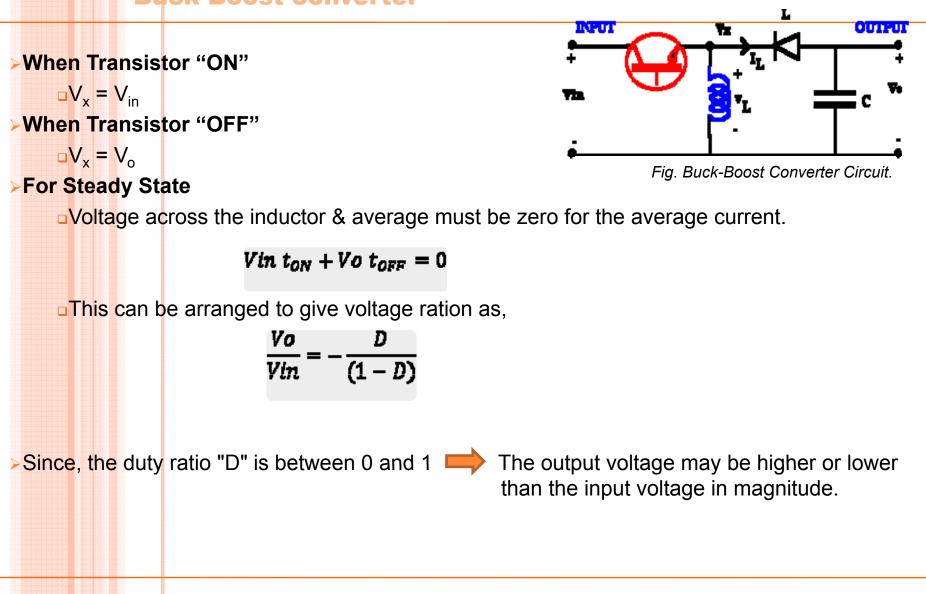

# Buck-Boost converter

IARDS

HIGHLY

EFFICIENT

MONOLITHIC DC/DC CON

#### **13**

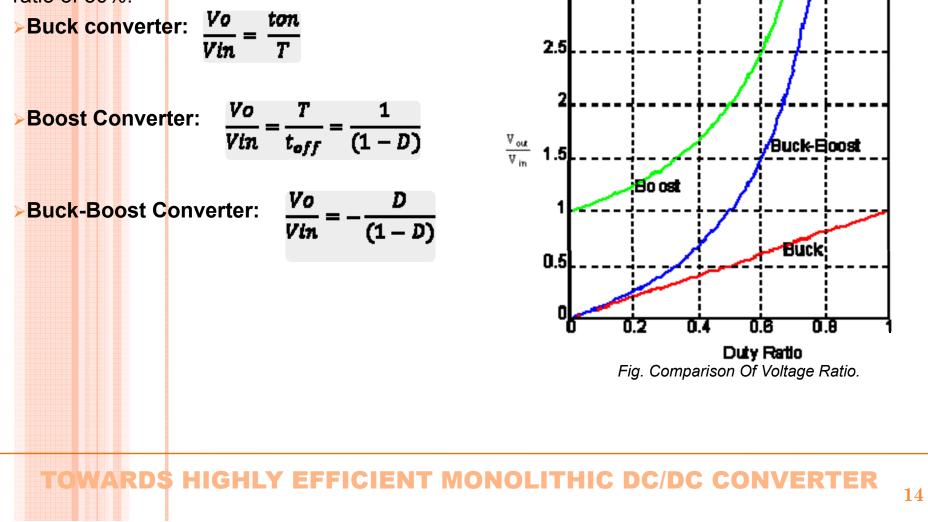

## **Comparison Of Different Converters**

>only the buck converter shows a linear relationship.

The buck-boost can reduce or increase the voltage ratio with unit gain for a duty ratio of 50%.

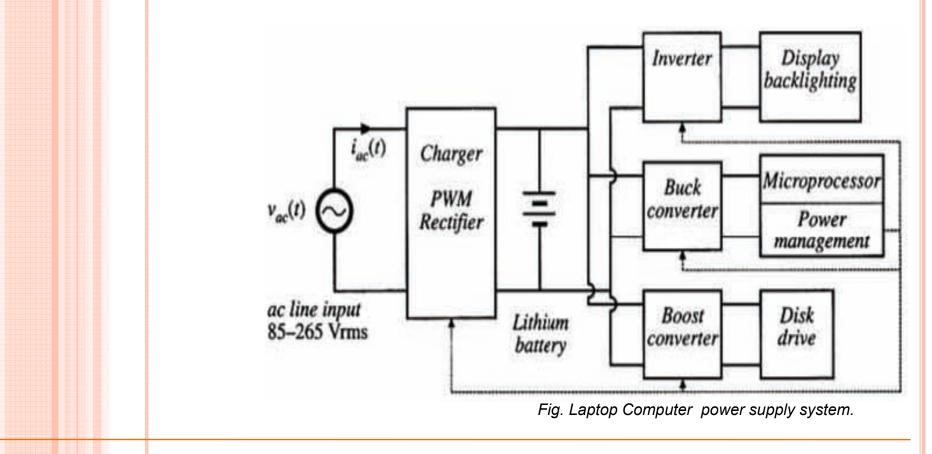

# **Monolithic Integrated DC/DC Converters**

### Why Monolithic DC/DC Converter?

Required for portable devices-laptops, mobiles etc.

- Decrease the size & weight of these devices.

- Miniaturization of the power modules.

Integrating a DC-DC converter can potentially lower the parasitic losses as interconnect b/w DC-DC converter & microprocessor is reduced.

□Need for on chip, point-of-load (PoL) power conversion.

### Challenges

Tight area constraint for the on-chip integration of inductive & capacitive elements.

>Poor parasitic impedance characteristics.

High frequency low value & physical size of passive devices required.

# **Monolithic Integrated DC/DC Converters**

### **Applications**

Battery operated portable electronic devices like Laptops, cell phones, PDAs (Personal digital assistants) & other palm devices.

### **Monolithic Integrated DC/DC Converters**

17

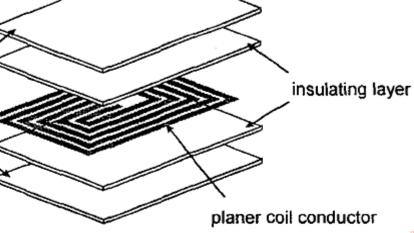

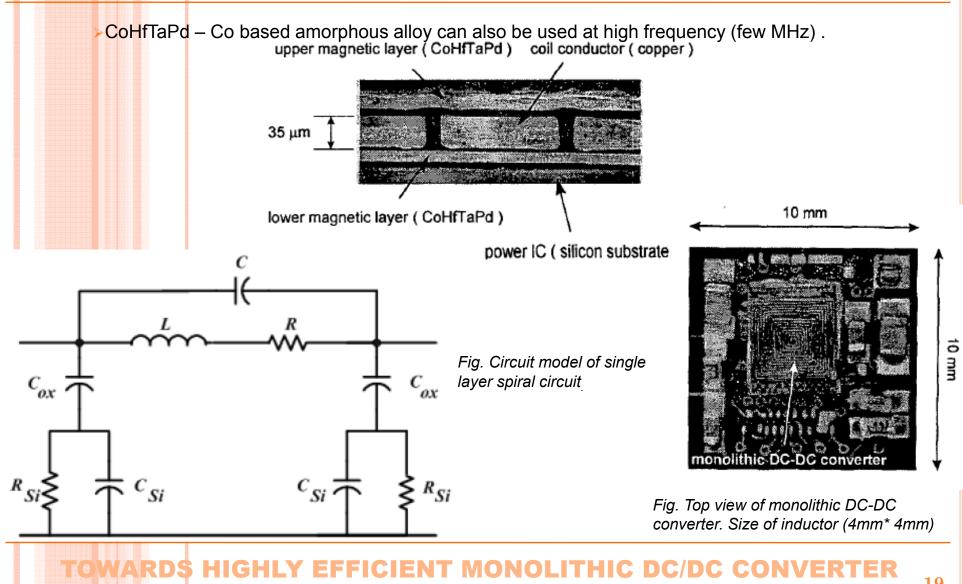

# **Power stage:** Inductors for On Chip DC/DC Converter (MHz Frequency)

magnetic layer

- >MEMS based inductors.

- Use iron-based alloy plated on Si substrate.

- Is a metal slab completely encapsulated by a magnetic material.

- Spirals made of 1µm AI-Cu isolated from ground plane by 0.5 µm of SiO<sub>2</sub>.

- The magnetic film surrounding metal is amorphous CoZrTa alloy that exhibits:

- small hysteresis losses.

- Withstand temperature up to 450°C.

- Integrated in standard high temperature CMOS Si process.

- **Cut off** frequency of approx. 1.4GHz.

- >Superior higher frequency & saturation characteristics.

- Reduces size & parasitic effects.

- Performs at frequency up to & beyond 10 MHz.

- Magnetic material below & above spirals prevent straying of magnetic flux.

- One layer of magnetic material increases inductance by 36-50% & two layers by 100-500%.

# **TOWARD\$ HIGHLY EFFICIENT MONOLITHIC DC/DC CONVERTER**

Fig. Schematic of Thin File Inductor.

# **Power stage:** Inductors for On Chip DC/DC Converter (MHz Frequency)

# **Power Stage:**Capacitors for On Chip DC/DC Converter (MHz frequency)

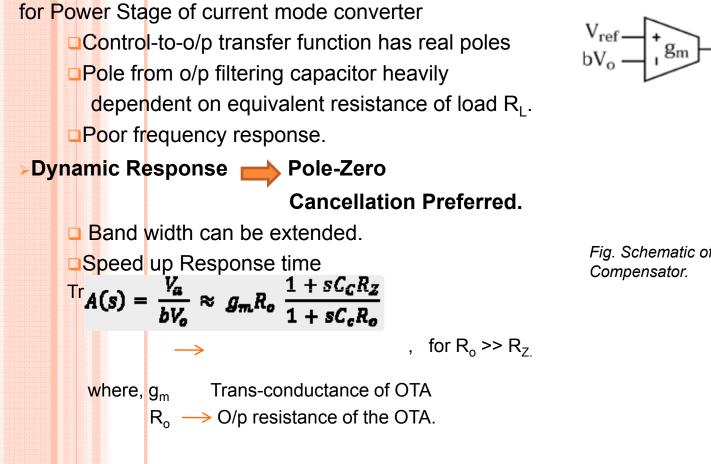

### Compensator

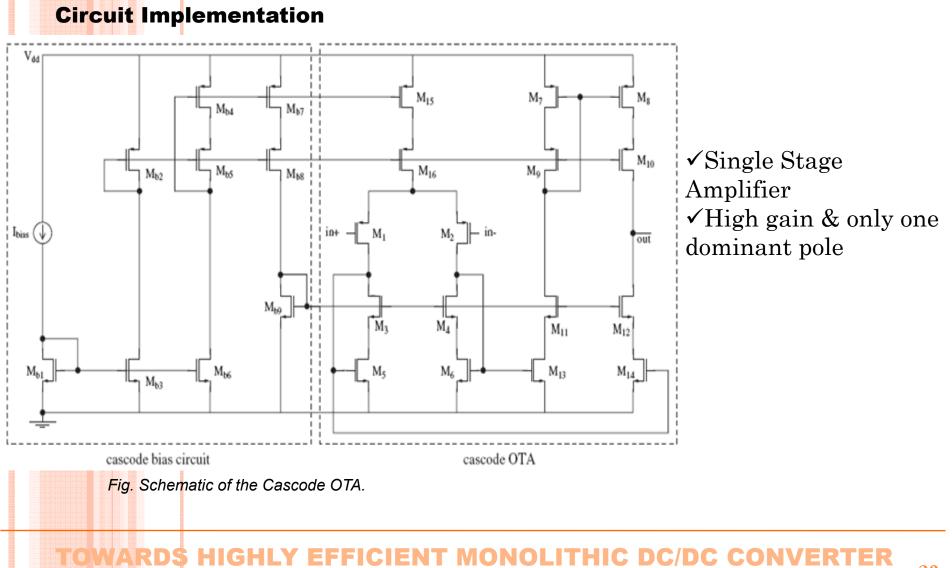

### **Cascode OTA (Operational Trans-conductance Amplifier)**

Fig. Schematic of Pole-Zero cancellation Compensator.

$R_{o}$

# TOWARD\$ HIGHLY EFFICIENT MONOLITHIC DC/DC CONVERTER

Va

$R_z$

### Compensator

- $>g_m \& R_o \implies$  important for frequency compensation

- → determine gain & phase margin of DC/DC converter

- $\rightarrow$  depend on biasing current

### **Result**

- Average -20 dB/dec closed loop-gain.

- Sufficient phase margin below unity gain frequency.

- ➤Two Stage OTA → Higher gain

- $\rightarrow$  Large output swing

## **Cascode OTA (Operational Trans-conductance Amplifier)**

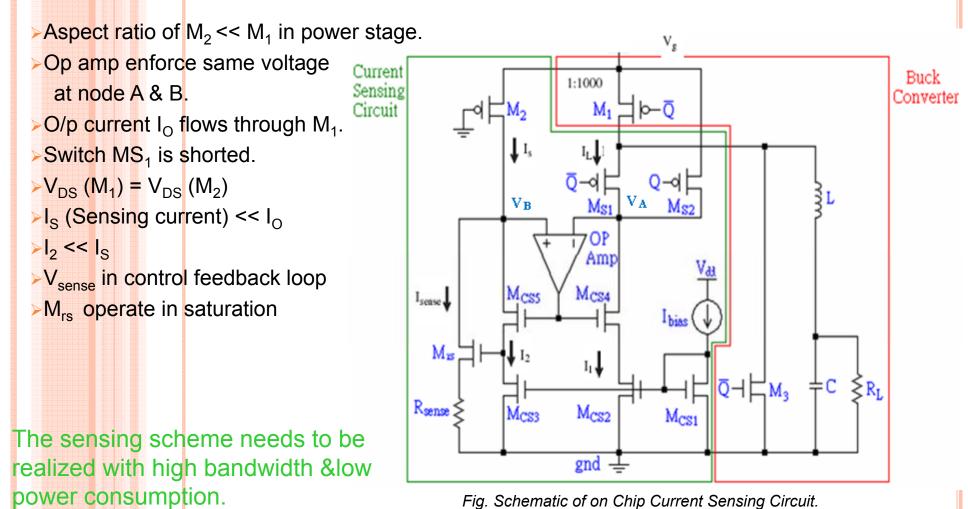

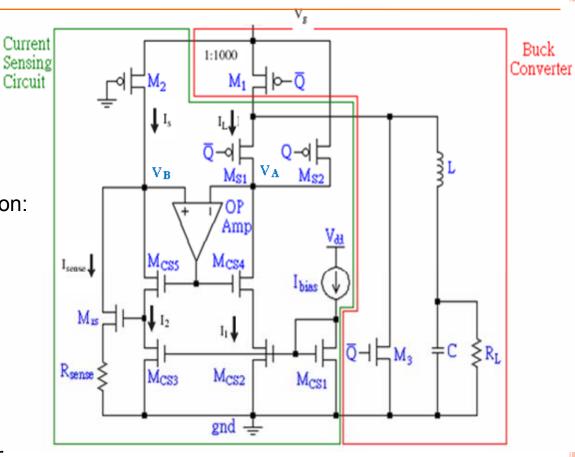

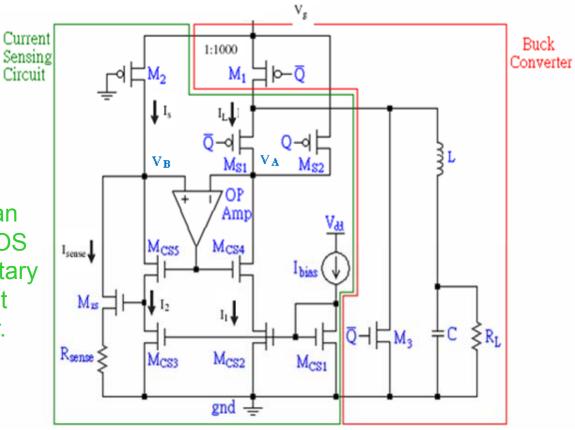

## **On Chip Current Sensing Technique (to Sense Inductor Signal)**

Fig. Schematic of on Chip Current Sensing Circuit.

TOWARDS HIGHLY DC/DC EFFI IENT HIC

# **On Chip Current Sensing Technique (to Sense Inductor Signal)**

### **Characteristics**

V<sub>sense</sub> =I<sub>sense</sub> R<sub>sense</sub> =I<sub>L</sub> R<sub>sense</sub> /1000

High gain amplifier required for accurate current sensing.

Accuracy of sensed current depend on:

current mirror M<sub>1</sub> & M<sub>2</sub>.

On-chip resistor R<sub>sense</sub>.

Matching of M<sub>1</sub> & M<sub>2</sub> depend on:

Mobility, µ

Oxide capacitance, C<sub>ox</sub>.

Threshold voltage, V<sub>T</sub>.

Location of M<sub>2</sub> to minimize error.

Fig. Schematic of on Chip Current Sensing Circuit.

## **On Chip Current Sensing Technique (to Sense Inductor Signal)**

### **Advantages**

I<sub>sense</sub> small Hence, power loss reduced in the sensing circuit.

Improve efficiency of converter.

On-chip current-sensing circuit can be extended to sense power NMOS transistor by building complementary circuit for other topologies – boost converter & buck-boost converter.

Fig. Schematic of on Chip Current Sensing Circuit.

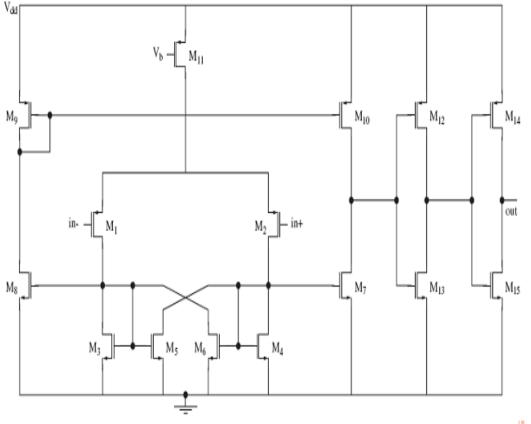

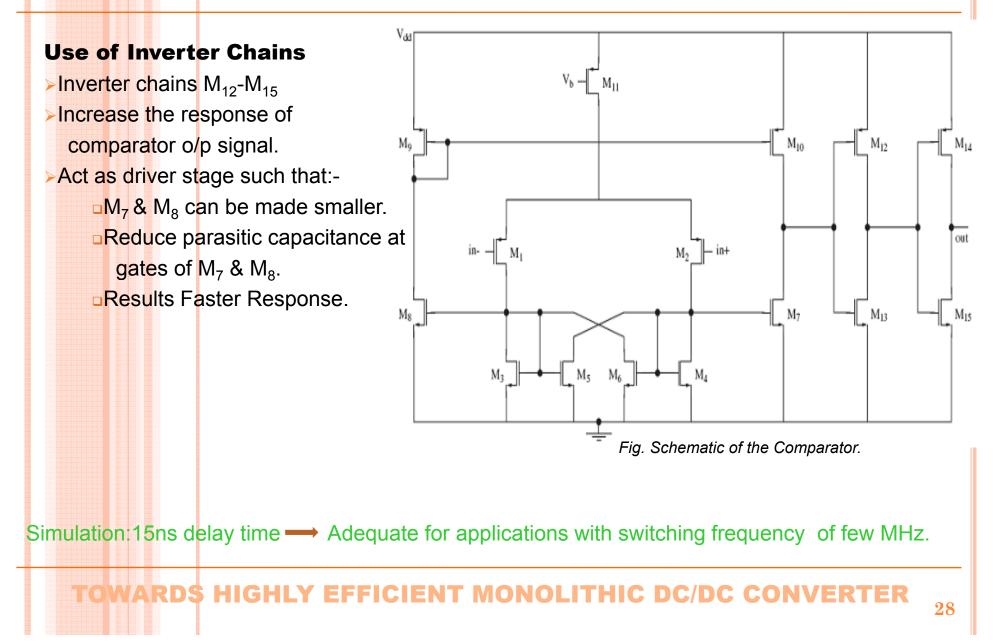

# **Modulator (Comparator)**

### Comparator

where, a =

- Needed in both:

- modulator in feedback control (PWM control).

- hysteretic comparator in the Oscillator & ramp generator circuit.

- Implemented by a source-coupled differential pair with positive feedback

to provide a high gain.

- Gain of positive feedback gain stage is:

$$A_{p} = \sqrt{\frac{\mu_{p}(\frac{W}{L})_{1}}{\mu_{n}(\frac{W}{L})_{2}}} \frac{1}{(1-\alpha)}$$

is the positive feedback factor.

Fig. Schematic of the Comparator.

### Comparator

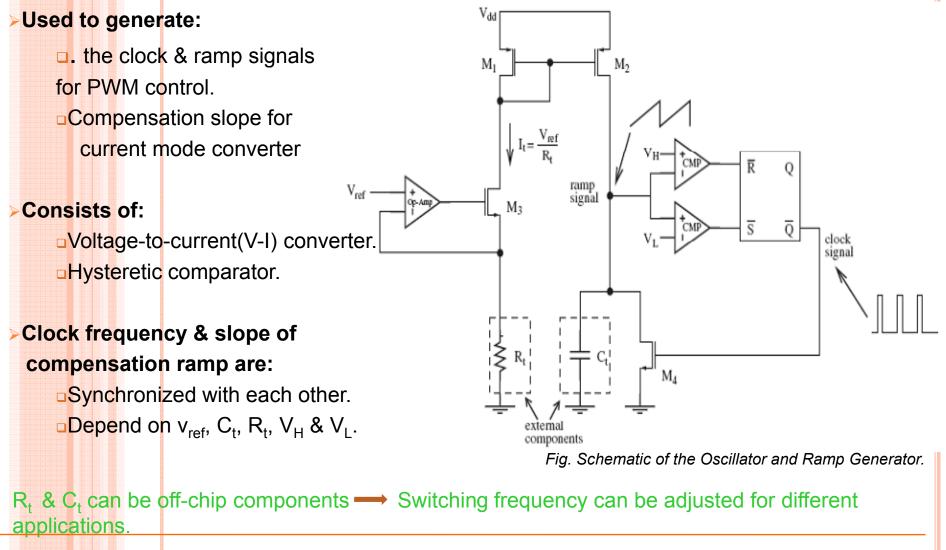

## **Oscillator and Ramp Generator**

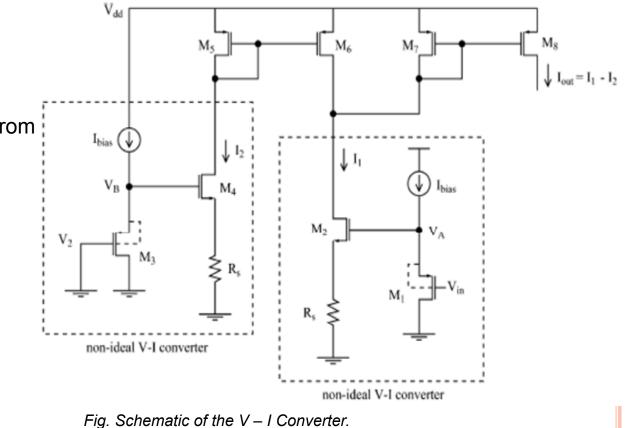

# **V-I Converter**

In current mode converters, compensation ramp add with inductor current signal to avoid sub harmonic oscillations.

- V-I designed to convert ramp signal & sensing inductor signal into current.

- V-I converter is a cascade of:

- 1. Source follower

- 2. Common-source config.

- I/p voltage of ramp vol.

- & sensing voltage range from 300-1000mV.

- Not high enough to turn

'ON' M<sub>2</sub> & M<sub>4</sub>.

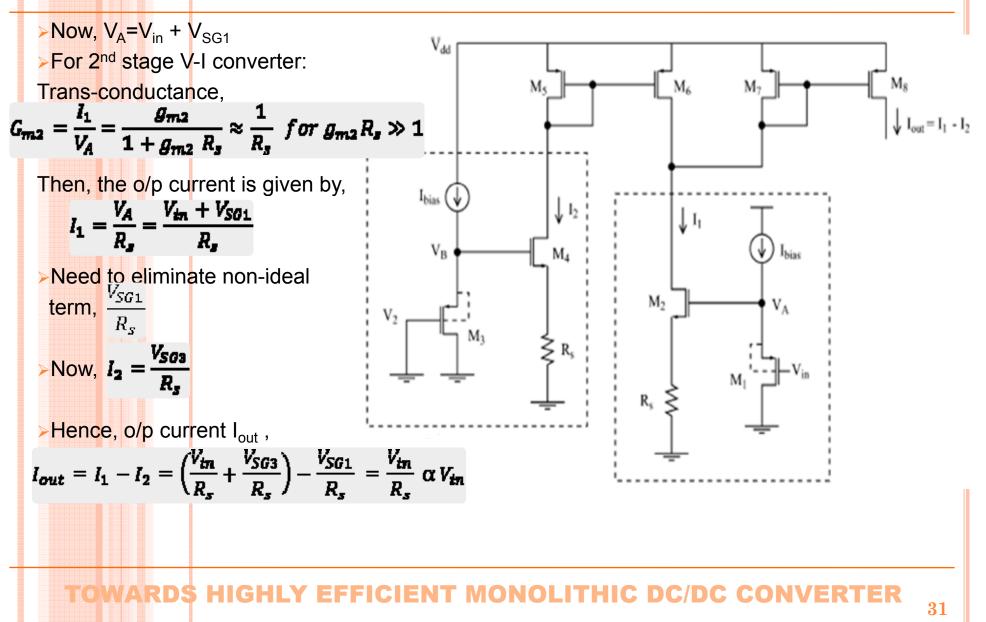

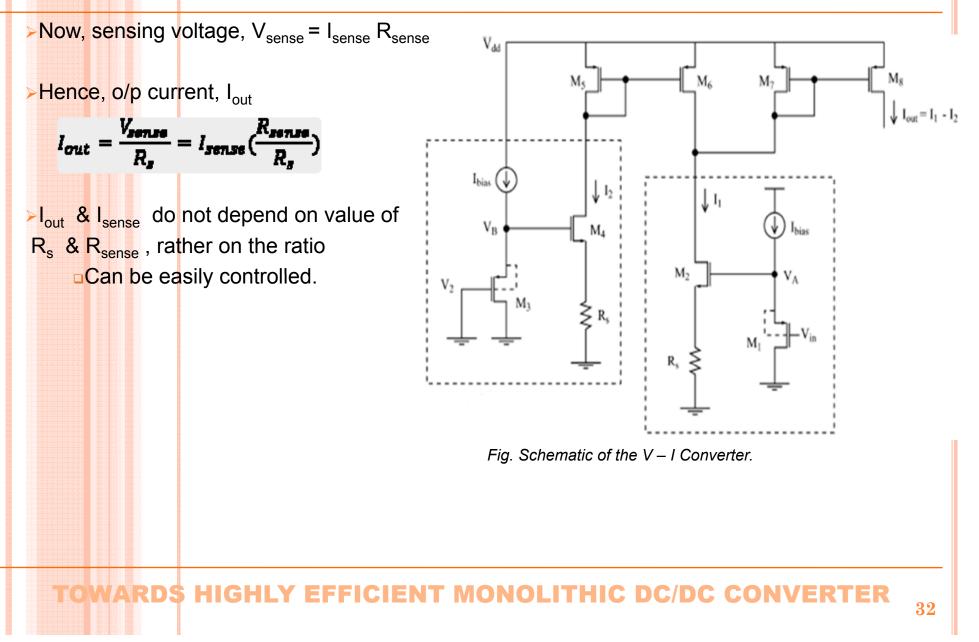

## **V-I Converter**

## **V-I Converter**

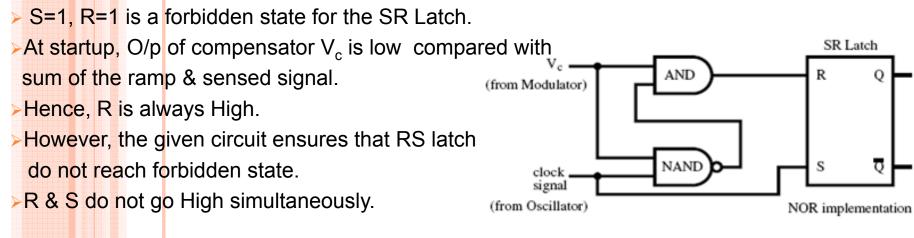

## **Pulse width Generator**

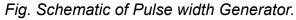

# **Buffer**

Required for receiving and amplifying the signal produced by the control circuit.

Poorly designed buffer with a simple inverter Chain a shoot-through current will occur and a large current will pass through the power transistors during each switching transition.

Hence, buffer without short-circuit power consumption is needed.

Power rails of the buffer should be

laid-out carefully & resistances to be minimized So that the converter efficiency do not degrade.

## **Power Losses in DC/DC Converter**

Conduction Loss

Switching Loss

Related to the size of Power Transistors Optimum Sizing required to improve Efficiency.

# Shoot through current Loss

Related to design of buffer Stage to drive power transistors.

Significant energy dissipated in parasitic impedances of circuit board inter connect & discrete components of the regulator.

Conduction Losses: Caused by the parasitic resistive impedances.

Switching Losses: Due to parasitic capacitive impedances of circuit components.

> Power consumed by PWM feedback circuit & integrated filter capacitor is small as compared to the power consumption of the power train (the power MOSFETs, MOSFET gate drivers, the filter inductor).

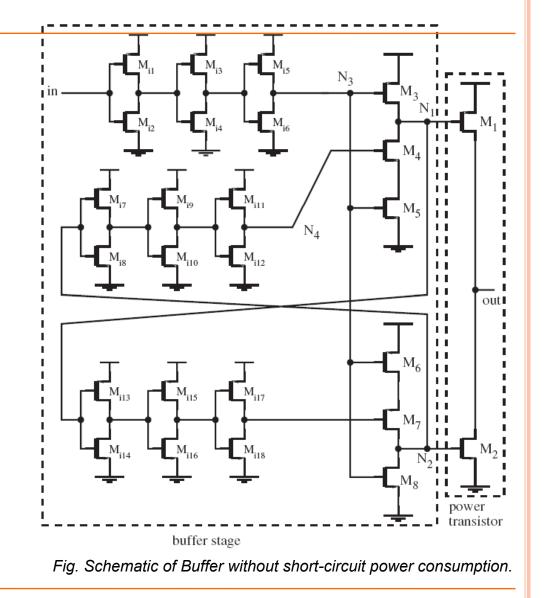

### **Power Flow Analysis in DC/DC Converter**

Buck converter O/p,  $V_{DD2}(t)=DV_{DD1} + V_{ripple}(t)$ . Ripple Current, ∆i = (V<sub>DD1</sub> – V<sub>DD2</sub>)D/2Lf<sub>s.</sub> Amplitude of voltage ripple,  $\Delta V_{DD2} = \frac{(V_{DD1} - V_{DD2})D}{16LC f_s^{\ 2}} = \frac{\Delta i}{8C f_s}$ where, L — Filter inductance. Filter Capacitor. С Switching frequency. f

Fig. Inductor Current  $i_L(t)$ , Output voltage  $V_{DD2}(t)$ , capacitor current  $i_C(t)$  waveforms.

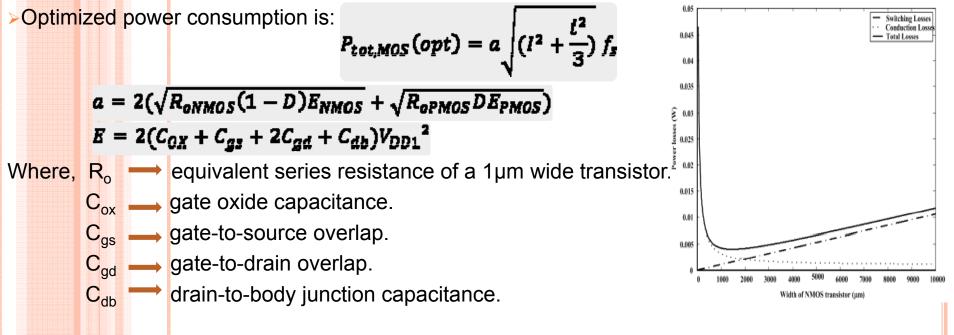

#### MOSEFETs Related Power

Combination of Conduction loss & Dynamic Switching loss.

- Dynamic Power Dissipated in each switching cycle of charging/discharging of Gate oxide, gate-to-source/drain overlap & drain-to-body junction capacitance of MOSFET.

MOSFET width optimized to minimize power dissipation.

#### **Filter Inductor Power**

R<sub>Lo</sub>

Energy consumption due to:

Series resistance of filter inductor.

Stray capacitance of filter inductor.

>Total power consumption in inductor is:

$$P_{tot,inductor} = b(\frac{l^2}{\Delta i f_s} + \frac{\Delta l}{3f_s} + \frac{C_{Lo}V_{DD1}^2}{R_{Lo}\Delta l})$$

$$b = \frac{(V_{DD1} - V_{DD2})DR_{Lo}}{2}$$

Where,  $C_{Lo} \rightarrow$  Parasitic stray capacitance per

Parasitic stray capacitance per nH Inductance.

Parasitic Series Resistance per nH Inductance.

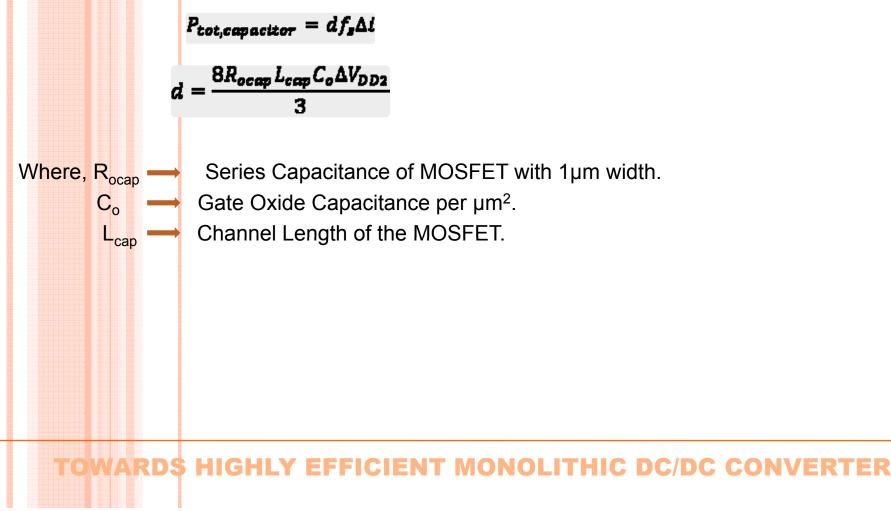

#### Filter Capacitor Related Power

Integrated Capacitor implemented utilizing Gate Oxide Capacitance of MOSFET

Total Power dissipation of a filter Capacitor is:

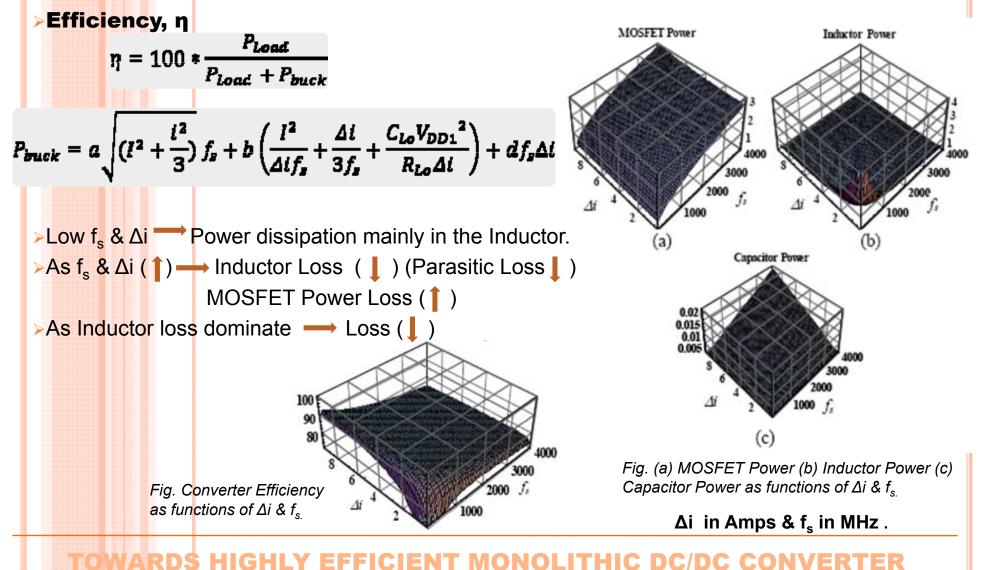

### **- Total Power Consumption of Buck Converter**

$$P_{buck} - P_{tot,MOS}(opt) + P_{tot,inductor} + P_{tot,capacitor}$$

$$P_{buck} = a \sqrt{\left(l^2 + \frac{i^2}{3}\right)} f_s + b \left(\frac{l^2}{\Delta i f_s} + \frac{\Delta i}{3 f_s} + \frac{C_{Lo} V_{DD1}^2}{R_{Lo} \Delta i}\right) + df_s \Delta i$$

>Strongly function of Switching frequency ( $f_s$ ) & Ripple Current ( $\Delta i$ ).

$\begin{array}{c} \mathsf{P}_{\mathsf{tot},\;\mathsf{capacitor}}(\begin{tabular}{l} \begin{tabular}{l} \mathsf{P}_{\mathsf{tot},\;\mathsf{inductor}}(\begin{tabular}{l} \mathsf{P}_{\mathsf{tot}}(\begin{tabular}{l} \mathsf{P}_{\mathsf{tot}}(\begi$

$P_{tot, capacitor} \longrightarrow Negligibly small (less than 1%) as compared to Inductor & MOSFET Power.$

## **Efficiency Analysis in DC/DC Converter**

## **Efficiency Analysis**

- Both the switching and conduction power dissipation of the power MOSFETs and the filter inductor increases.

- → thereby degrading the efficiency.

## Major challenges for a monolithic switching DC-DC converter

□The area occupied by the integrated filter capacitor.

The effect of the parasitic impedance characteristics of the integrated inductors on the overall efficiency characteristics of a switching DC-DC converter.

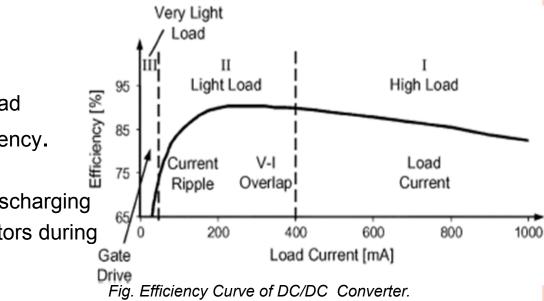

# Light Load Efficiency in DC/DC Converter (to Improve Efficiency)

- Battery-powered portable electronic devices like cell phones, Laptops etc.

- Full loading not present for prolonged periods.

- Rather devices run at light loads (Stand-By mode) for most of the time.

#### Region I

Conduction Losses dominate.

#### Region II

Switching Losses proportional to load

Current, i/p voltage, switching frequency.

#### Region III

Gate-drive losses while charging/discharging Gate Capacitances of Power transistors during Switching transition.

#### **Decreasing Switching Frequency Best way to Reduce Total Loss**.

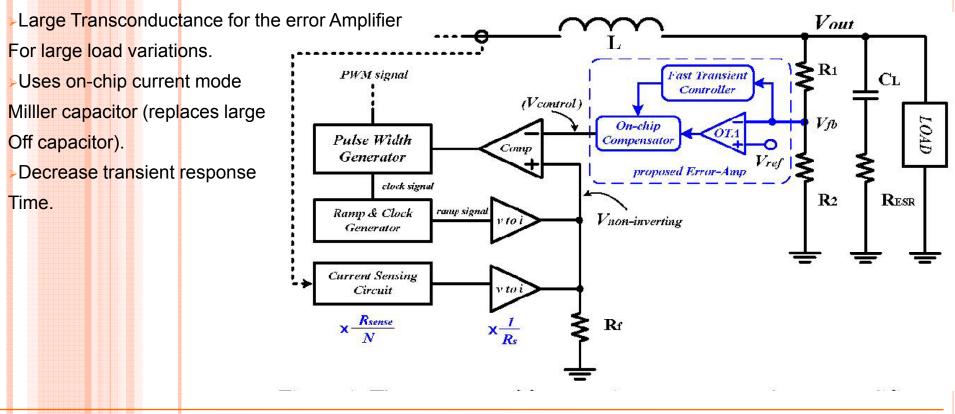

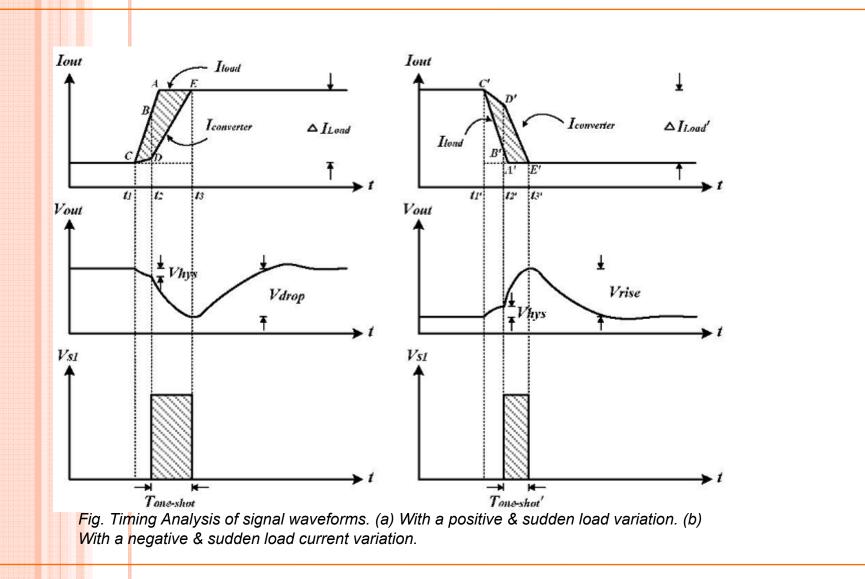

## **Compensated Error Amplifier (for Fast Transient Response)**

Fast transient response of o/p voltage reveals critical point for large load variations. Required to supply reliable voltage.

## Solution

## **Compensated Error Amplifier (for Fast Transient Response)**

# **Compensated Error Amplifier (for Fast Transient Response)**

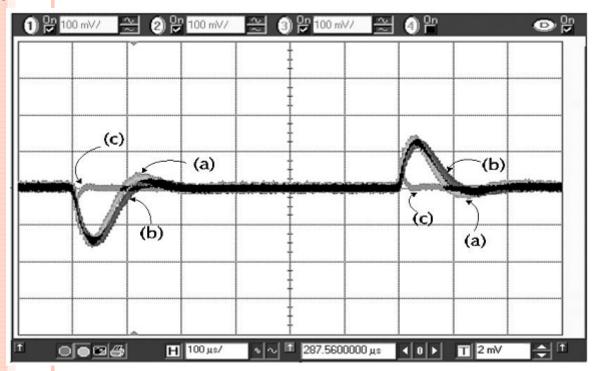

#### >Better Response Time.

Fig. The transient response with load current step b/w 100mA & 400mA. (a) Conventional error amplifier. (b) On-chip compensated error amplifier without fast transient controller. (c) On-chip compensated error amplifier with fast transient controller.

# **Issues with Monolithic DC/DC Converters**

- High Efficiency with large input voltage range.

- High Performance System-on-chip (SOC) systems

- Dynamic Power Management

- Fast Dynamic Response

- Low Power Consumption: low stand by power.

- Need to provide robust Output Voltage regulation

- Maximum Efficiency

- Minimize Ripple noise on Input & Output

- <mark>≻Minimize c</mark>ost

- To have accurate sensed current for current mode PWM controller

- Reduce supply voltage demand, greater amount of current from external power supplies.

- Voltage scaling capability.

## References

#### **Books**

R.W. Erickson, "Fundamentals of Power electronics"; Kluwer academic Publications, N.J. USA, 2<sup>nd</sup> Edition, 2001.

#### **Research Papers**

- 1. C.F. Lee, P.K.T Mok; "A Monolithic Current-Mode CMOS DC–DC Converter With On-Chip Current-Sensing Technique", IEEE journal of Solid-State circuits, vol. 39, issue-1, Jan. 2004, pp. 3-14.

- 2. V. Kursun, S.G. Narendra, V.K. De, E.G. Friedman; "Low-Voltage-Swing Monolithic dc–dc Conversion", IEEE transactions on circuits and systems, vol. 51, issue 5, May 2004, pp. 241-248.

- V. Kursun, S.G. Narendra, V.K. De, E.G. Friedman; "Analysis of Buck Converters for On-Chip Integration With a Dual Supply Voltage Microprocessor", IEEE transactions on VLSI systems, vol. 11, issue 3, June 2003, pp. 514-522.

- Y. Katayama, S. Sugahara, H. Nakazawa, M. Edo; "High-Power-Density MHz Switching Monolithic DC-DC Converter with Thin-Film Inductor", IEEE 31<sup>st</sup> Annual Power Electronics Specialists Conference 2000, vol. 3, 18<sup>th</sup>-23<sup>rd</sup> June 2000, pp. 1485-1490.

- S. Zhou, G.A.R. Mora; "A High Efficiency, Soft Switching DC–DC Converter With Adaptive Current-Ripple Control for Portable Applications", IEEE transactions on circuits and systems, vol. 53, issue 4, April 2006, pp. 319-323.

- H.W. Huang, H.H. Ho, C.C. Chien, K.H. chen, G.K. Ma, S.Y. Kyo; "Fast Transient DC-DC Converter with On-Chip Compensated Error Amplifier", Proceedings of the 32<sup>nd</sup> European solid-State Circuits Conference 2006, sept. 2006, pp. 324-327.

# Questions???

# THANK YOU !!!